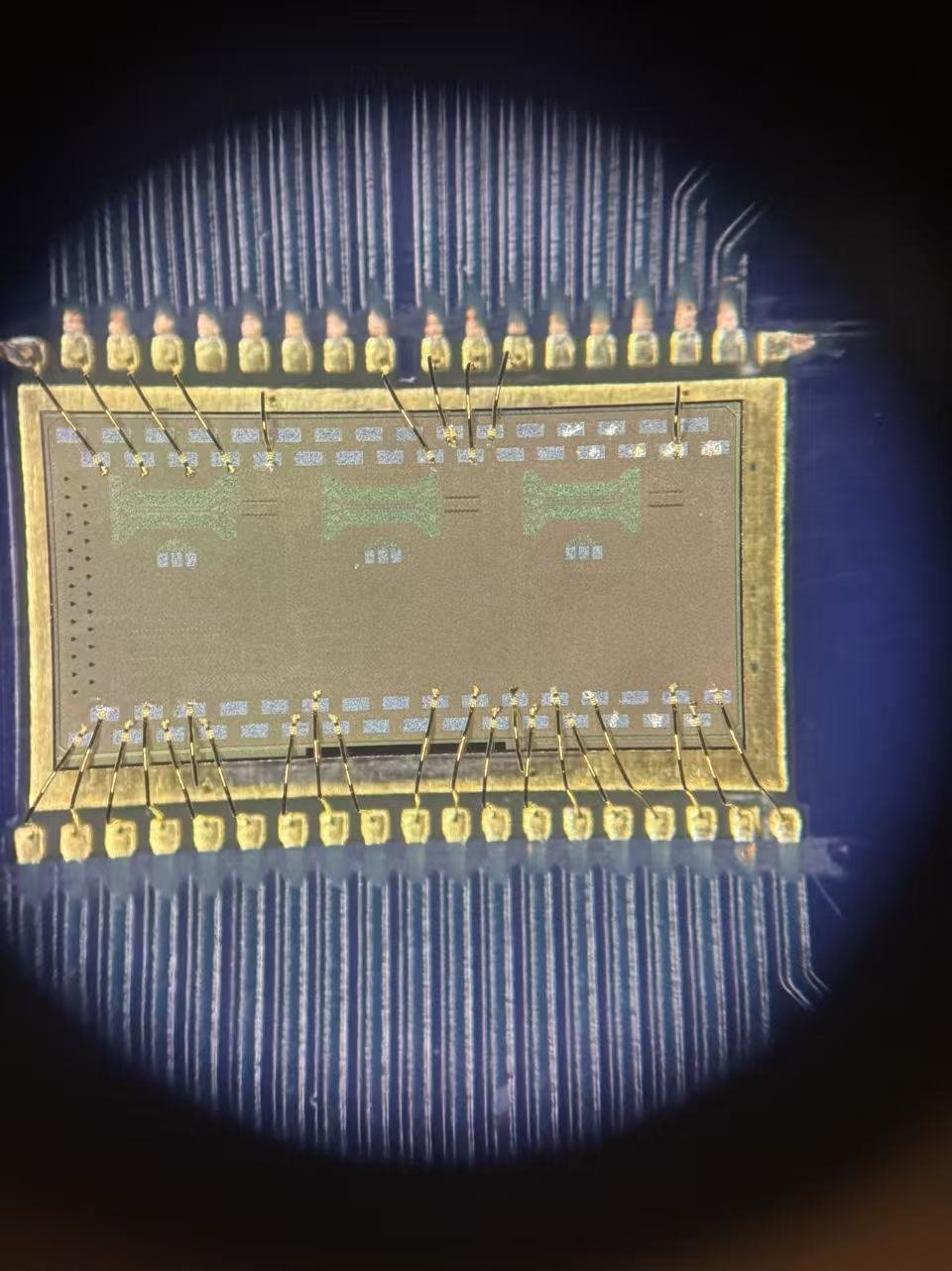

Cryogenic Electronic Layer · TYN-E

Logic at base temperature.

Standard CMOS still works at 4 K — at the cost of a small shift in transistor behavior — and that's the trick TYNANA's controller exploits. Built in 22nm FD-SOI, the cryo-CMOS die decodes incoming pulses, drives gate waveforms through low-noise DACs, and pipes measurement results back through an ADC and amplifier chain.

Because logic and gating sit a few centimeters from the qubits, real-time correction loops can close in under a microsecond — which is what fault-tolerant operation actually needs.

- Process22nm FD-SOI · GF22FDX

- Operating temp4 K (controller) · <100 mK (driver tier)

- Pulse DAC14-bit · 1 GS/s

- Readout ADC12-bit · 500 MS/s