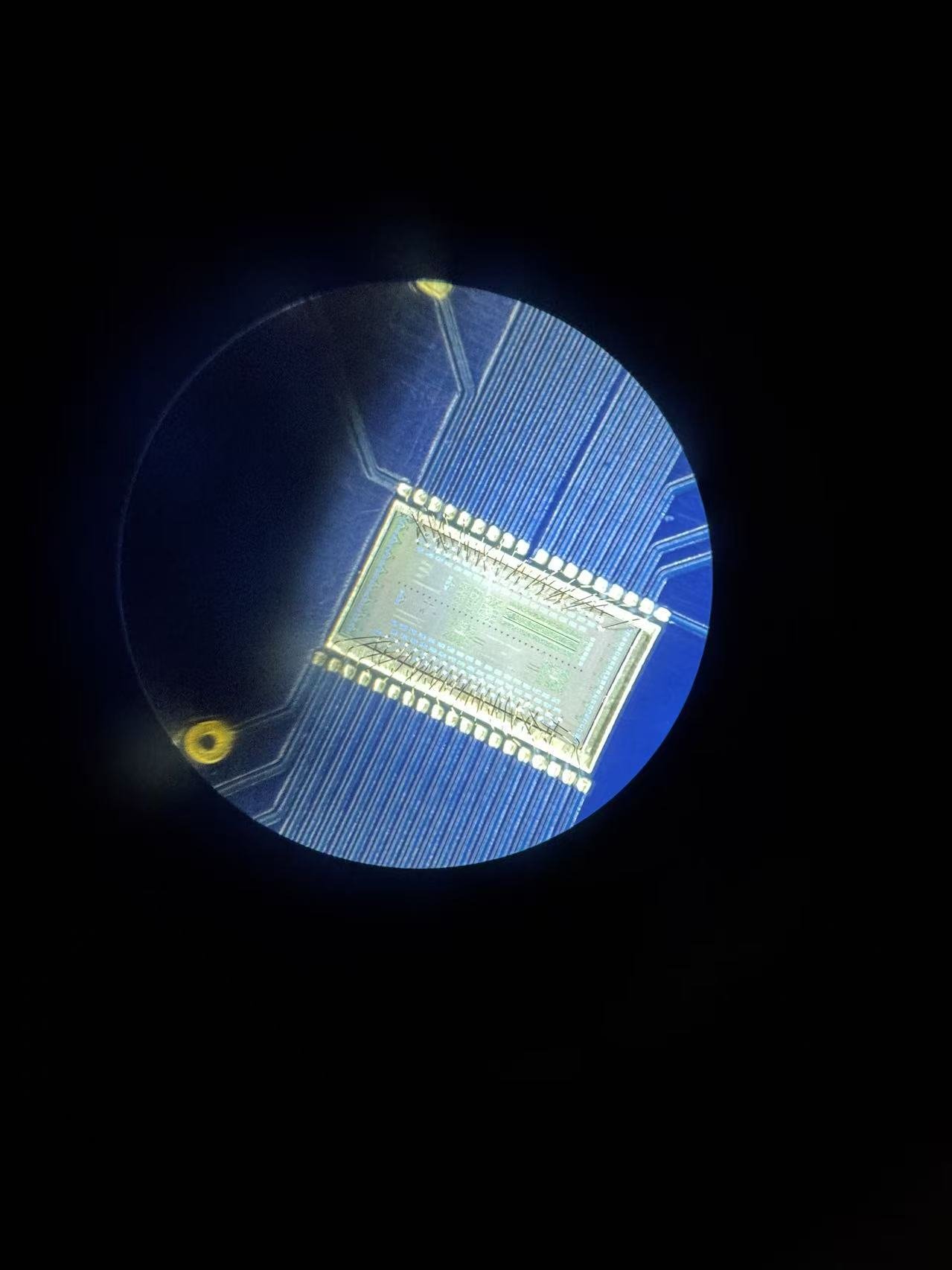

Architecture meets silicon.

The story Tynana tells is not a paper architecture. The cryo-CMOS controller die is wire-bonded onto a custom routing PCB, with the trace network fanning out to test instrumentation. This is the level of physical readiness the architecture has reached today — not a render, an actual board on the bench.